# **ROS-25 User Manual**

# Version 2.0

J. M. Cela, C. Fernández, C. Willmott.

Electrónica y Automática. CIEMAT.

January 27<sup>th</sup>, 2008.

# **INDEX**

| 1 Introduction                                             | 4     |

|------------------------------------------------------------|-------|

| 2 ROS-25 Connections                                       | 6     |

| 3 Sector Collector Crate                                   | 12    |

| 4 Overview of the ROS-25 design                            | 15    |

| 5 ROS-25 VME Interface                                     | 18    |

| 5.1 Memory access : A24 access, word width                 | 18    |

| 5.2 Registers access: A16 access, word width               | 19    |

| 6 ROS-25 Configuration                                     | 37    |

| 6.1 Mode of operation: Memory readout                      | 37    |

| 6.2 Check status                                           | 39    |

| 7 Interface to the VOLTAGE, CURRENT AND TEMPERATURE SENSO. | RS 41 |

| 7.1 I2C interface through the PCA9564                      | 42    |

| 7.2 1-Wire Interface to the DS2438 through the DS2482      | 44    |

| 8 Interface to the GOL                                     | 52    |

| 8.1 Procedure for accessing the GOL                        | 54    |

| 9 ROS-25 Data Formats                                      | 55    |

| 9.1 ROS-25 Control words                                   | 55    |

| 9.2 ROS-25 Debugging data                                  | 57    |

| 9.3 Generated at HPTDC, modified by ROS-25.                | 58    |

| 9.4 Sector Collector Trigger Data                          | 60    |

| 10 Apendix A: Data generated at the HPTDC (ROB)            | 61    |

| 11 References                                              | 63    |

#### 1 INTRODUCTION

In this manual it is explained the basic functionality of the Read-Out Server (ROS) board. This board performs the second level of read-out in the data acquisition chain of the muon drift tube system of CMS. Its main task is the management of digitalized data that comes from the Read-Out Boards (ROB), located inside the Minicrates, attached to the drift tube chambers. Each ROS board can handle up to 25 input channels (up to 25 ROBs), storing data and performing a data merging event by event for further optical transmission to next level of the DAQ chain, the DDU.

In the following figure, a general scheme of the read-out chain of the drift tubes subdetector is presented:

Figure 1: Diagram of the Drift Tubes read-out chain.

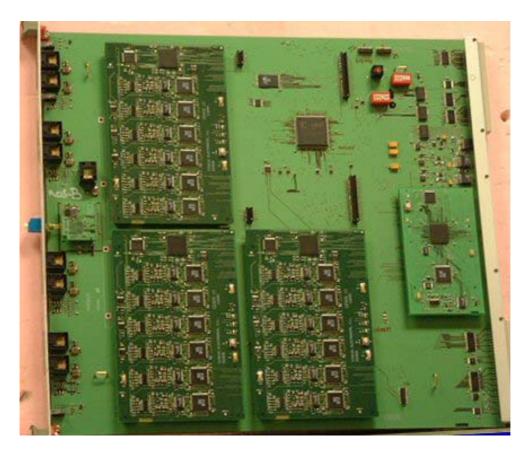

The ROS board is a 9U VME board, 400 mm depth with 8 RJ-45 input connectors and one optical output. Apart from transmission of received data through the optical output, the ROS has a spy memory where a programmed amount of events can be stored for further reading through a VME interface.

Figure 1: Picture of a Read-Out Server board.

#### 2 ROS-25 CONNECTIONS

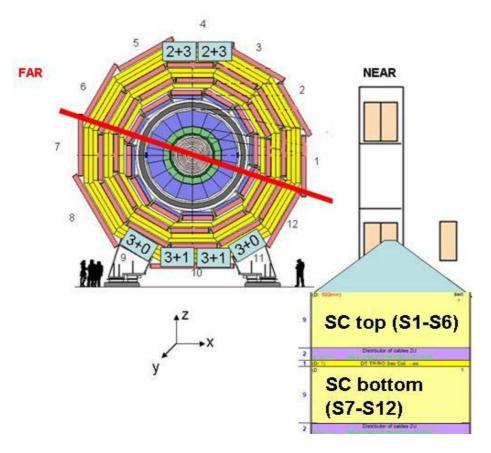

ROS boards will be located in two crates (TOP and BOTTOM) of the DT & RPC TRIGGER RACK (X2J22, X2J12, X2J02, X2V12, X2V22), that is, the outer rack of the lowest near balcony of each wheel. There will be 6 ROS per crate, named from ROS1 to ROS12, one per sector.

In principle, each wheel is subdivided in an upper part (sectors 1 to 6) that are connected to the ROSs of the TOP crate and a bottom part (sectors 7 to 12) connected to the ROSs of the BOTTOM crate.

Figure 2: View of the two Sector Collectors crates for one CMS wheel.

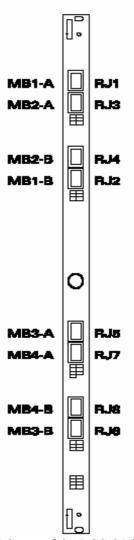

Minicrate to Read-Out Server (ROS) links have been distributed in order to minimize the required number of connectors on the ROS while maintaining a unique ROS board format for every sector. The ROS board has been designed with 25 channels to read in average one full sector, and each ROS has 8 RJ-45 connectors with some of its pairs operational according to the following tables:

| Connector | Number of links | Cable | Coming from           |

|-----------|-----------------|-------|-----------------------|

| RJ1       | 3               | MB1-A | MB1 (ROB 0 to 2)      |

| RJ2       | 3               | MB1-B | MB1 (ROB 3* to 5)     |

| RJ3       | 3               | MB2-A | MB2 (ROB 0 to 2)      |

| RJ4       | 3               | MB2-B | MB2 (ROB 3 to 5)      |

| RJ5       | 4               | MB3-A | MB3 (ROB 0 to 3)      |

| RJ6       | 3               | MB3-B | MB3 (ROB 4 to 6)      |

| RJ7       | 3               |       | Depends on the sector |

| RJ8       | 3               |       | Depends on the sector |

Note: \* ROB 3 of MB1 is a ROB-32 (32 channels instead of 128).

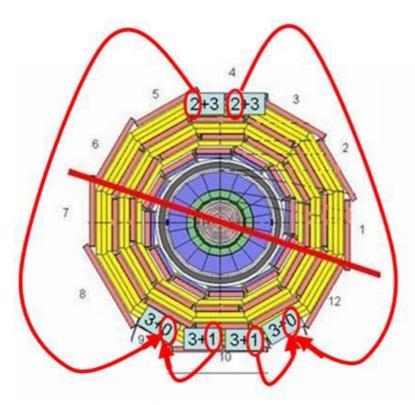

At sectors 1, 2, 3, 5, 6, 7, 8 and 12, connectors RJ7 and RJ8 are related to MB4(ROB 0 to 2) and MB4(ROB 3 to 5) respectively, but as sectors 4 and 10 have two chambers MB4 each, the extra channels have been accommodated in the ROS boards reading sectors 9 and 11 that have fewer channels. A patch panel is attached to the Sector Collector crate to allow interconnection. Final scheme for connectors RJ7 and RJ8 is presented in the following table:

|                                      | Con-<br>nector | Number of links | (     | Cables                         | Coming from                                                |

|--------------------------------------|----------------|-----------------|-------|--------------------------------|------------------------------------------------------------|

| ROS for                              | RJ7            | 3               | MB4-A | MB4(s)-1                       | 3 from MB4 (ROB 0 to 2)                                    |

| sectors<br>(1,2,3,5,6,7<br>8 and 12) | RJ8            | 3               | MB4-B | MB4(s)-2                       | 3 from MB4 (ROB 3 to 5)                                    |

| ROS 4                                | RJ7            | 3               | MB4-A | MB4(4)3-2                      | 3 from MB4(4)3 (ROB 2 to 4)                                |

| KOS 4                                | RJ8            | 3               | MB4-B | MB4(4)5-2                      | 3 from MB4(4)5 (ROB 2 to 4)                                |

|                                      | RJ7            | 3               | MB4-A | MB4(9)-1                       | 3 from MB4(9) (ROB 0 to 2)                                 |

| ROS 9                                | RJ8            | 3               | MBX   | MB4(4)5-1 + MB4(10)9-2         | 2 from MB4(4)5 (ROB 0 and 1)<br>+ 1 from MB4(10)9 (ROB 3)  |

| ROS 10                               | RJ7            | 3               | MB4-A | MB4(10)11-<br>1                | 3 from MB4(10)11 (ROB 0 to 2)                              |

|                                      | RJ8            | 3               | MB4-B | MB4(10)9-1                     | 3 from MB4(10)9 (ROB 0 to 2)                               |

|                                      | RJ7            | 3               | MB4-A | MB4(11)-1                      | 3 from MB4(11) (ROB 0 to 2)                                |

| ROS 11                               | RJ8            | 3               | MBY   | MB4(4)3-1 +<br>MB4(10)11-<br>2 | 2 from MB4(4)3 (ROB 0 and 1)<br>+ 1 from MB4(10)11 (ROB 3) |

|             | SECTOR |            |           |       |            |       |             |       |             |       |

|-------------|--------|------------|-----------|-------|------------|-------|-------------|-------|-------------|-------|

| ROS Channel | 1,2,3, | 5,6,7,8,12 | 4         |       | 9          |       | 10          |       | 11          |       |

| 0           | MB1    | ROB 0      | MB1       | ROB 0 | MB1        | ROB 0 | MB1         | ROB 0 | MB1         | ROB 0 |

| 1           | MB1    | ROB 1      | MB1       | ROB 1 | MB1        | ROB 1 | MB1         | ROB 1 | MB1         | ROB 1 |

| 2           | MB1    | ROB 2      | MB1       | ROB 2 | MB1        | ROB 2 | MB1         | ROB 2 | MB1         | ROB 2 |

| 3           | MB1    | ROB 3      | MB1       | ROB 3 | MB1        | ROB 3 | MB1         | ROB 3 | MB1         | ROB 3 |

| 4           | MB1    | ROB 4      | MB1       | ROB 4 | MB1        | ROB 4 | MB1         | ROB 4 | MB1         | ROB 4 |

| 5           | MB1    | ROB 5      | MB1       | ROB 5 | MB1        | ROB 5 | MB1         | ROB 5 | MB1         | ROB 5 |

| 6           | MB2    | ROB 0      | MB2       | ROB 0 | MB2        | ROB 0 | MB2         | ROB 0 | MB2         | ROB 0 |

| 7           | MB2    | ROB 1      | MB2       | ROB 1 | MB2        | ROB 1 | MB2         | ROB 1 | MB2         | ROB 1 |

| 8           | MB2    | ROB 2      | MB2       | ROB 2 | MB2        | ROB 2 | MB2         | ROB 2 | MB2         | ROB 2 |

| 9           | MB2    | ROB 3      | MB2       | ROB 3 | MB2        | ROB 3 | MB2         | ROB 3 | MB2         | ROB 3 |

| 10          | MB2    | ROB 4      | MB2       | ROB 4 | MB2        | ROB 4 | MB2         | ROB 4 | MB2         | ROB 4 |

| 11          | MB2    | ROB 5      | MB2       | ROB 5 | MB2        | ROB 5 | MB2         | ROB 5 | MB2         | ROB 5 |

| 12          | MB3    | ROB 0      | MB3       | ROB 0 | MB3        | ROB 0 | MB3         | ROB 0 | MB3         | ROB 0 |

| 13          | MB3    | ROB 1      | MB3       | ROB 1 | MB3        | ROB 1 | MB3         | ROB 1 | MB3         | ROB 1 |

| 14          | MB3    | ROB 2      | MB3       | ROB 2 | MB3        | ROB 2 | MB3         | ROB 2 | MB3         | ROB 2 |

| 15          | MB3    | ROB 3      | MB3       | ROB 3 | MB3        | ROB 3 | MB3         | ROB 3 | MB3         | ROB 3 |

| 16          | MB3    | ROB 5      | MB3       | ROB 5 | MB3        | ROB 5 | MB3         | ROB 5 | MB3         | ROB 5 |

| 17          | MB3    | ROB 6      | MB3       | ROB 6 | MB3        | ROB 6 | MB3         | ROB 6 | MB3         | ROB 6 |

| 18          | MB4    | ROB 0      | MB4-4 (3) | ROB 2 | MB4        | ROB 0 | MB4-10 (11) | ROB 0 | MB4         | ROB 0 |

| 19          | MB4    | ROB 1      | MB4-4 (3) | ROB 3 | MB4        | ROB 1 | MB4-10 (11) | ROB 1 | MB4         | ROB 1 |

| 20          | MB4    | ROB 2      | MB4-4 (3) | ROB 4 | MB4        | ROB 2 | MB4-10 (11) | ROB 2 | MB4         | ROB 2 |

| 21          | MB4    | ROB 3      | MB4-4 (5) | ROB 2 | MB4-4 (5)  | ROB 0 | MB4-10 (9)  | ROB 0 | MB4-4 (3)   | ROB 0 |

| 22          | MB4    | ROB 4      | MB4-4 (5) | ROB 3 | MB4-4 (5)  | ROB 1 | MB4-10 (9)  | ROB 1 | MB4-4 (3)   | ROB 1 |

| 23          | MB4    | ROB 5      | MB4-4 (5) | ROB 4 | MB4-10 (9) | ROB 3 | MB4-10 (9)  | ROB 2 | MB4-10 (11) | ROB 3 |

| 24          | MB3    | ROB 4      | MB3       | ROB 4 | MB3        | ROB 4 | MB3         | ROB 4 | MB3         | ROB 4 |

| 25          |        | SC         | SC        |       | SC         |       | SC          |       | SC          |       |

Here, MB4(4)5 stands for Minicrate MB4 from sector 4 that is closest to sector 5, and MB(4)3, the closest to sector 3. Idem for MB4(10)9 and MB4(10)11.

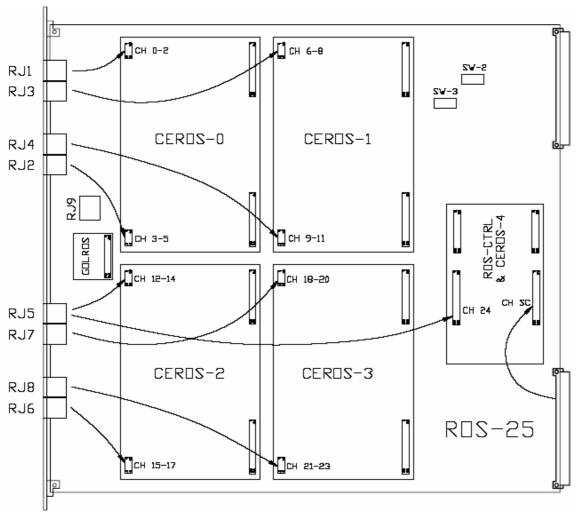

In the following diagram the front panel of the ROS-25 is shown. Note that connectors are not in consecutive order.

Figure 3: Scheme of the ROS-25 front panel.

POner fotos del patch panel MBX, MBY XXX

Figure XX: Mapping of ros channels from sector 4 and sector 10 to sector 9 and sector 11.

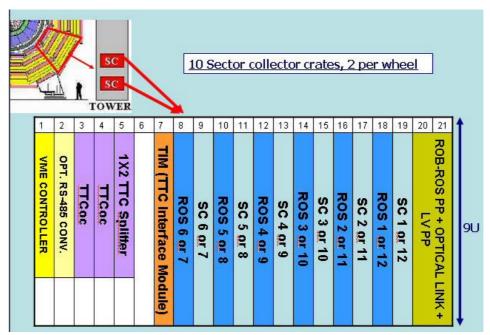

#### **3 SECTOR COLLECTOR CRATE**

The preliminary layout of each crate is presented in figure 4. Inside each crate there will be: 6 ROS boards, 6 Sector Collector boards, a TIM board [5] a 3U VME controller and 3 TTC [3] boards for splitting and fan-out of the TTC optical signal to the Minicrates and also to the Sector Collector crate. And finally, the crate will also include a patch panel for grouping ROB-ROS channels and the connectors for the 5V power supply of the Sector Collector crate.

Figure 4: Diagram of the Sector Collector crate and the different boards at each slot.

The TIM module is a 9U board used for receiving the optical TTC signal and retransmitting the decoded information to the ROS and the Sector Collector boards through a 3U and 13 slots backplane located in the bottom part of the crate.

Through the TIM backplane the following TTC signals are retransmitted:

- L1A

- Bunch counter reset

- Event counter reset

- Bunch counter value at the corresponding L1A (12 bits).

- Event counter value at the corresponding L1A (24 bits).

- Other B-Go commands for the Sector Collector board.

It has to be noted that by default the ROS will read the Bunch and Event counter values from the TIM backplane and not from an internal counter. These values are decoded at the TTCrx device at each TIM board.

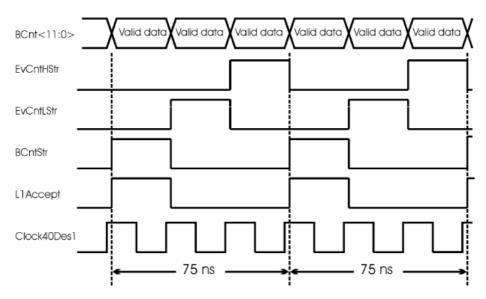

In order to obtain proper values of these two counters at the ROS and SC, the TTCrx has to be operated in trigger mode "11" (as it is by default), that is, there cannot be two consecutive triggers separated in less than 75 ns, or in other words, the maximum L1A frequency is 13.33MHz. The following picture clarifies this requirement, however, for more information you can have a look at the TTCrx user manual [6].

Figure 5: Trigger mode "11" at the TTCrx.

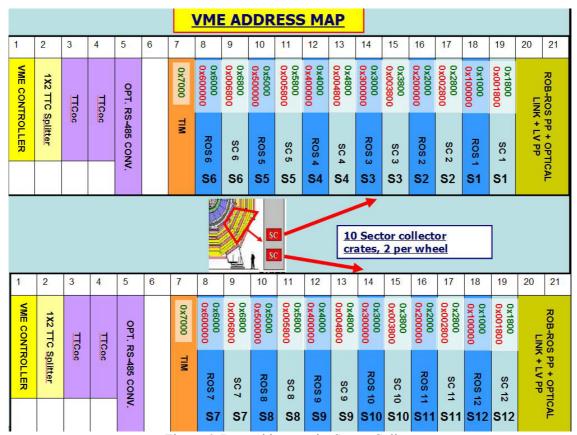

# 3.1 Base Address

The base address are the Sector Collector crate are arranged in the following order:

Figure 6: Base address at the Sector Collector crate.

#### 4 OVERVIEW OF THE ROS-25 DESIGN

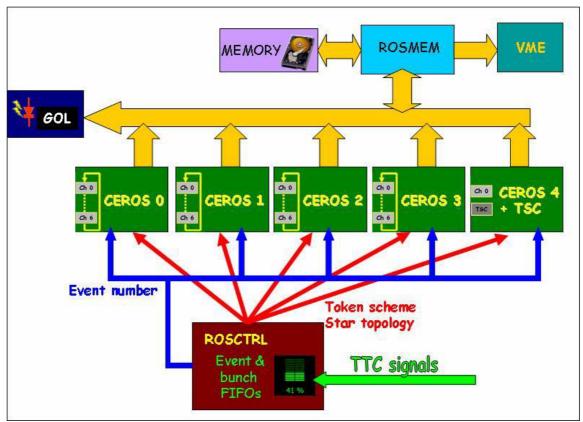

At the ROS, the 25 channels are grouped in blocks of 6 channels, controlled by an FPGA device that performs the read-out of these channels and checks whether the channels are locked, there are parity errors, etc. Each of these groups of 6 channels is called a CEROS, and there are four of these functional blocks in a ROS as can be seen in figure 2.

There is also a fifth CEROS functional block (CEROS 4) that handles only 1 input channel, number 25<sup>th</sup>. It is identical to the other four CEROS but only for 1 channel.

Figure 5: Diagram of the ROS-25 with its main piggy boards.

Another functional module in the ROS is called ROSCTRL. This module contains: first of all, the "Sector Collector channel", and second, the control of the whole read-out functionality.

In certain modes of operation, it may be desired to read the Sector Collector trigger data within the DAQ data flow. Therefore, each Sector Collector board will send, at each event, their

data to its contiguous ROS in the crate, and these data will be treated by the ROS as if it was another input channel, the 26<sup>th</sup>.

Finally, we can find also the GOLROS module, the last functional block in the ROS which includes the GOL serializer and the VCSEL optical transmitter.

Figure 5: Diagram of the ROS architecture.

Related to how the read-out is performed, the ROS can be programmed in different modes of operation:

#### • Normal operation mode:

Event and bunch information is received from the TTC system and stored in 255 words FIFOs. Events are processed in parallel in each group of 6 channels (CEROS). Data is sent to a common bus following a token ring scheme for serialization and optical transmission to the DDU through an optical link.

#### • Spy mode:

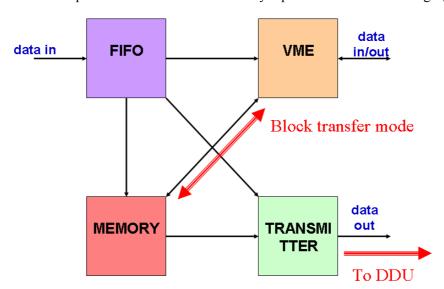

Besides sending the data to the DDU, the ROS can store a programmable number of words or of events in a spy memory 512 kBytes long. This memory can be accessed through a VME interface in normal or block transfer mode. This mode of operation can be used in parallel with normal operation mode, it does not interfere.

#### • Transmission test mode (GOL TEST):

Through a VME interface, data can be written in the internal ROS memory and then sent through the optical transmitter to the DDU. The number of words sent and also the average bandwidth can be selected.

#### • Straight FIFO read-out:

This mode of operation has been implemented for debugging purposes, where data are read through VME directly from the input FIFOs. In this way, the format of the data will be the same that comes from the HPTDC, as the ROS is almost transparent in this operation mode.

These different operation modes are schematically represented in the following figure:

Figure 6: ROS-25 functional diagram.

# 5 ROS-25 VME INTERFACE

The ROS-25 supports different access modes:

| Access type                                         | Data Width     | Minimum address space needed |                                       |

|-----------------------------------------------------|----------------|------------------------------|---------------------------------------|

| Short non-privileged A16                            | Word (16 bits) | 1024 words<br>(0x400)        | Access to all of the ROS-25 registers |

| Standard A24 non-<br>privileged                     | Word (16 bits) | 256 kwords<br>(0x40000)      | Access to the memory.                 |

| Standard A24 standard non-privileged block transfer | Word (16 bits) | 256 kwords<br>(0x40000)      | Access to the memory.                 |

The A16 base address is selected with switch SW3, (A15-A10), and the A24 address is selected with switch SW2, (A23-A20). The address mapping for the registers of the different functional blocks is what follows:

| A16 Base Address<br>(A15 – A10) | Functional<br>block |

|---------------------------------|---------------------|

| Base Address + 0x00             | CEROS0              |

| Base Address + 0x80             | CEROS1              |

| Base Address + 0x100            | CEROS2              |

| Base Address + 0x180            | CEROS3              |

| Base Address + 0x200            | CEROS4              |

| Base Address + 0x280            | ROSCTRL             |

| Base Address + 0x300            | MEMCTRL             |

| Base Address + 0x380            | ROSVME              |

# 5.1 Memory access: A24 access, word width

It can be standard or non-privileged block data transfer.

Address from 0x00000 to 0x7FFFE (256kwords = 262144 words)

| )-15 Memory Data | R/W |

|------------------|-----|

|------------------|-----|

### 5.2 Registers access: A16 access, word width.

#### **5.2.1 ROSVME**

All the registers from ROSVME are not reset by a global reset but by a local reset, except for the registers belonging to the PCA9564 device.

#### Control y status (ROSVME + 0x00)

Default value = 0x7D

Reset by a hard reset.

| bits | description                                 | acc |                                   |

|------|---------------------------------------------|-----|-----------------------------------|

| 0    | ROS waiting                                 | R   | 1 = ROS has finished processing   |

|      |                                             |     | an event.                         |

| 1    | Memory Done                                 | R   | 1 = programmed limit achieved     |

| 2-6  | FPGA's programmed                           | R   | 1 = corresponding FPGA            |

|      |                                             |     | properly programmed               |

| 7    | '0'                                         | R   |                                   |

| 8    | Enable EVCNT_reset to perform a soft reset. | R/W |                                   |

| 9    | Select GOL clock                            | R/W | 0 = ckdesv1, 1 = ckdesv2          |

| 10   | Select ROS-25 clock                         | R/W | 0 = ckdesv1, 1 = ckdesv2          |

| 11   | Load PAF values in all the FIFOs            | W   |                                   |

| 12   | Partial CEROS FIFO reset (PRS)              | W   | Will also be executed with a soft |

|      |                                             |     | reset.                            |

| 13   | Master CEROS FIFO reset (MRS)               | W   | Will also be executed with a hard |

|      |                                             |     | reset.                            |

| 14   | Hard reset                                  | W   |                                   |

| 15   | Soft reset                                  | W   |                                   |

A VME sys-reset will force also a hard reset and will also reprogram the FPGAs (by hardware).

Bits 9 and 10 select among the two output clocks from the TTCrx device with their corresponding programmed de-skew. As the output of the ckdesv2 signal is disabled at the TTCrx device by default and for the ROS-25 prototypes it is not recommended to use ckdesv2, we do not recommend writing a 1 in any of those two bits. (The last does not apply to the ROS-25 prototype at Torino).

#### **Soft reset is executed by:**

- Writing 0x8000 in register ROSVME+0x00.

- When receiving an Event Reset signal from the TTC system if it is enabled in bit 8 of ROSVME+0x00.

- Whenever a hard reset is executed.

#### Hard reset is executed by:

- Writing 0x4000 in register ROSVME+0x00.

- When a sysreset is received from the VME controller.

# $\underline{SPAF/SFF(ROSVME + 0x04)}$ Default value: 0x00

Reset by a hard reset.XXX?

| bits | description | acc |                                                                |

|------|-------------|-----|----------------------------------------------------------------|

| 0-4  | SPAF        | R   | 1 = Almost Full flag active in any of the FIFOs of each CEROS. |

| 5-9  | SFF         | R   | 1 = Full flag active in any of the FIFOs of each of the CEROS. |

#### Interruptions (ROSVME + 0x06)

$\overline{Default = 0x\ 20}$

Reset by a hard reset.

| bits | Description                                | acc |                                        |

|------|--------------------------------------------|-----|----------------------------------------|

| 0    | enable SPAF interrupt                      | R/W | If any of the FIFOs signals the almost |

|      |                                            |     | full flag (PAF), an interruption will  |

|      |                                            |     | take place.                            |

| 1    | enable SFF interrupt                       | R/W | If any of the FIFOs gets full at any   |

|      |                                            |     | time, an interruption will take place. |

| 2    | enable memory done interrupt (rising edge) | R/W | 1                                      |

|      |                                            |     | ROS has achieved the programmed        |

|      |                                            |     | condition (number of words/events to   |

|      |                                            |     | be transmitted/stored on memory).      |

| 3    | enable ROS waiting interrupt (rising edge) | R/W | 1                                      |

|      |                                            |     | ROS finishes processing an event. To   |

|      |                                            |     | be used only in normal or spy mode.    |

| 4    | interrupt requested                        | R   | = 1 An interruption from the ROS has   |

|      |                                            |     | occurred.                              |

| 5-7  | interrupt level                            | R/W |                                        |

| 8-15 | interrupt vector                           | R/W |                                        |

### $FPGA \ Control \ (ROSVME + 0x08)$

Default value = 0x1000Reset by a hard reset.

| bits  | description                                   | acc |                                     |

|-------|-----------------------------------------------|-----|-------------------------------------|

| 0-4   | FPGAs INIT signal                             | R/W | If the INIT bit is set to one,      |

|       |                                               |     | whenever that FPGA is               |

|       |                                               |     | reprogrammed it will be standing    |

|       |                                               |     | in erase mode until the INIT bit is |

|       |                                               |     | released.                           |

| 5-9   | Reprogram the FPGAs                           | W   | When writing a 1 here, the FPGAs    |

|       |                                               |     | are reprogrammed                    |

| 10-12 | Select clock frequency for loading FPGAs from | R/W |                                     |

|       | their program memories                        |     |                                     |

| 13    | Enables reprogramming FPGAs with an event     | R/W |                                     |

|       | reset signal.                                 |     |                                     |

| 14 | Enables reprogramming FPGAs with a soft reset | R/W |  |

|----|-----------------------------------------------|-----|--|

|    | signal.                                       |     |  |

Note: FPGA load clock frequency:

- 000 1,25 MHz

- 001 2.5 MHz

- 010 5 MHz

- 011 10 MHz

- 100 20 MHz (default)

- Others  $\Rightarrow$  1,25 MHz

#### JTAG Control (ROSVME + 0x0A)

Default value = 0x7

Reset by a hard reset.

| bits | description                                                   | acc |

|------|---------------------------------------------------------------|-----|

| 0-2  | Selection of the device to be configured through connector J1 | R/W |

- 0 Configure CEROS 0

- 1 Configure CEROS 1

- 2 Configure CEROS 2

- 3 Configure CEROS 3

- 4 Configure ROSCTRL

- 5 Configure ROSMEM

- 6 Configure devices through VME (The device to configure has to be selected afterwards in register ROSVME+0x0C).

- 7 Device selected from corresponding position of switch SW1.

#### $\underline{JTAG\ Register\ 1\ (ROSVME + 0x0C)}$

Default value = 0x0

Reset by a hard reset.

| bits | description                             | acc |

|------|-----------------------------------------|-----|

| 0-3  | Enables JTAG access to each CEROS FLASH | R/W |

| 4    | Enables JTAG access to ROSCTRL FLASH    | R/W |

| 5    | Enables JTAG access to ROSMEM           | R/W |

| 6    | flash_tck                               | R/W |

| 7    | flash_tms                               | R/W |

| 8    | flash_tdi                               | R/W |

| 9-14 | flash tdo                               | R   |

# JTAG TDI Register 2 (ROSVME + 0x0E)

Default value = 0x0Reset by a hard reset.

| bits | description            | acc |

|------|------------------------|-----|

| 7-0  | Flash TDI (7 downto 0) | R/W |

| 8    | Flash TMS              | R/W |

| 12-9 | Bits to send (max 8)   | R/W |

The state machine to send the TDI bits is activated as soon as anything is written in this register.

#### JTAG TDO Data (ROSVME + 0x10)

Default value = 0x0

Reset by a hard reset.

| bits | description                                           | acc |

|------|-------------------------------------------------------|-----|

| 0-7  | Sequence of bits received (TDO) (bit 0 last received) | R   |

| 8    | Finished                                              |     |

#### <u>12C & 1-wire & GOL & OPLL (ROSVME + 0x12)</u>

Default value = 0xA4Reset by a hard reset.

| bits | description                 | acc |                                                        |  |

|------|-----------------------------|-----|--------------------------------------------------------|--|

| 0    | Enable I2C access to GOL    | R/W |                                                        |  |

| 1    | Enable I2C access to I,V, T | R/W |                                                        |  |

|      | sensors                     |     |                                                        |  |

| 2    | GOL power off               | R/W | After a hard reset the GOL will be switched OFF.       |  |

| 3    | GOL ready                   | R   | =1 ok.                                                 |  |

| 4    | QPLL error registered       | R   | A SEU error occurred at the QPLL.                      |  |

| 5    | QPLL locked                 | R   | =1 ok.                                                 |  |

| 6    | QPLL unlocked registered    | R   | =1 at some point the QPLL has unlocked.                |  |

| 7    | GOL not ready registered    | R/W | =1 at some point the GOL was not ready.                |  |

| 8    | QPLL reset                  | W   |                                                        |  |

| 9    | Clock selected              | R   | =0 Clock is being received from the backplane. (Normal |  |

|      |                             |     | operation mode)                                        |  |

|      |                             |     | =1 Clock is coming from the internal ROS 40 MHz        |  |

|      |                             |     | crystal.                                               |  |

| 10   | Clock selected_reg          | R/W | =1, at some point the clock has come from the internal |  |

|      |                             |     | ROS 40 MHz crystal.                                    |  |

| 11   | GOL reset                   | W   |                                                        |  |

Bits 0 and 1 can not be enabled at the same time, so if ever a 1 is written on both at the same time, only the access to the I, V, T sensors will be enabled.

#### Note that:

#### **QPLL** is reset:

- Writing a 1 in bit 8 of ROSVME+0x12.

- With a hard reset.

#### **GOL** is reset:

- Writing a 1 in bit 11 of ROSVME+0x12.

- With a hard reset.

#### $\underline{PCA}$ STATUS (ROSVME + 0x20)

| bits | description | acc | default |

|------|-------------|-----|---------|

| 0-7  | Status      | R   | 0xF8    |

| 0-7  | Time-out    | W   | 0xFF    |

# $\underline{PCA} \ DATA \ (ROSVME + \theta x22)$

Default = 0x00

| bits | description | acc |

|------|-------------|-----|

| 0-7  | Data        | R/W |

#### $\underline{PCA} \ \underline{ADDRESS} (ROSVME + 0x24)$

$\overline{\text{Default}} = 0x00$

|     | description |     |

|-----|-------------|-----|

| 0-7 | Own address | R/W |

#### $\underline{PCA}$ CONTROL (ROSVME + 0x26)

$\overline{Default = 0x00}$

| bits | description | acc | Description             |

|------|-------------|-----|-------------------------|

| 7    | AA          | R/W | Assert acknowledge flag |

| 6    | ENSIO       | R/W | SIO enable bit          |

| 5    | STA         | R/W | Start flag              |

| 4    | STO         | R/W | Stop flag               |

| 3    | SI          | R/W | Serial interrupt flag   |

| 2-0  | CR          | R/W | Serial clock rate       |

CR: Serial clock frequency

| 000 | 330 kHz |

|-----|---------|

| 001 | 288 kHz |

| 010 | 217 kHz |

| 011 | 146 kHz |

|-----|---------|

| 100 | 88 kHz  |

| 101 | 59 kHz  |

| 110 | 44 kHz  |

| 111 | 36 kHz  |

The I2C protocol is reset with a hard reset.

#### **5.2.2 ROSMEM**

#### Control y status (ROSMEM + 0x00)

Default value = 0x00Reset by a hard reset.

| bits | description                                                                                  | acc |  |  |  |

|------|----------------------------------------------------------------------------------------------|-----|--|--|--|

| 0    | Enables transfer from memory to GOL. Mode GOL_TEST. If only this bit is set to 1, an         | R/W |  |  |  |

|      | unlimited transfer takes places. It can be stopped again by writing a 0 into this bit.       |     |  |  |  |

| 1    | Enables storing FIFOs data in ROS memory (SPY MODE). Any of bits 2, 3 or 4 should            | R/W |  |  |  |

|      | also be selected. The storage can also be forced to stop by writing a 0 again into this bit, |     |  |  |  |

|      | in such a case, if limit by number of events is selected, the ROS will stop to write on the  |     |  |  |  |

|      | memory as soon as the actual event is completed.                                             |     |  |  |  |

| 2    | Limits transfer by number of words. For GOL_TEST or SPY MODE.                                | R/W |  |  |  |

| 3    | Limits transfer by number of events. Only for SPY MODE.                                      | R/W |  |  |  |

| 4    | Enables transfer until memory full. For mode GOL TEST or SPY MODE. 262143 F                  |     |  |  |  |

|      | words will be sent or written into the memory.                                               |     |  |  |  |

| 5    | Enables repeat cycles of number of words for sending data to the transmitter. Only for       | R/W |  |  |  |

|      | mode GOL_TEST.                                                                               |     |  |  |  |

| 6    | Selects random transmission enable for GOL TEST mode of operation.                           | R/W |  |  |  |

| 7-10 | Enables corresponding LFSR register for random transmission enable. Only for mode            | R/W |  |  |  |

|      | GOL_TEST.                                                                                    |     |  |  |  |

The transmitter enable signal that loads the 16 bit words data into the GOL transmitter is generated by default in GOL\_TEST mode as a 20 MHz clock, obtaining therefore a bandwidth of 320 Mbps.

If bit 6 is set to 1, then, a random transmitter enable signal can be chosen. This random signal is obtained as the output of some pseudo-random shift registers (LFSR). Bits 7 to 10 enable each a LFSR register, and the transmitter enable signal is obtained as the logical AND of each of the enabled LFSR.

As these LFSR run at 40 MHz, the average frequency is also 20 MHz. By enabling more LFSRs the average bandwidth can be reduced to something more similar to the expected value during normal ROS operation mode: (~100 Mbps)

1 LFSR enabled: 20 MHz => 320 Mbps 2 LFSR enabled: 10 MHz => 160 Mbps 3 LFSR enabled: 5 MHz => 80 Mbps 4 LFSR enabled: 2,5 MHz => 40 Mbps

#### Memory pointer low (ROSMEM + 0x02)

Default value = 0x00Reset by a hard reset.

| bits | description                        | acc |

|------|------------------------------------|-----|

| 0-13 | Memory address pointer (bits 0-15) | R/W |

#### <u>Memory pointer high (ROSMEM + 0x04)</u>

Default value = 0x00Reset by a hard reset.

| bits | Description                         | acc |

|------|-------------------------------------|-----|

| 0-1  | Memory address pointer (bits 16-17) | R/W |

| 2    | Resets the memory pointer           | W   |

The memory pointer gives the number of 16 bit words stored in the memory.

#### Max word (16 bits) count low (ROSMEM + 0x06)

Default value = 0x00

Reset by a hard reset.

| bits | Description                         | acc |

|------|-------------------------------------|-----|

| 0-15 | Maximum number of words (bits 0-15) | R/W |

#### Max word (16 bits) count high (ROSMEM + 0x08)

Default value = 0x00

Reset by a hard reset.

| bits | Description                                  | acc |

|------|----------------------------------------------|-----|

| 0-1  | Maximum number of 16 bits words (bits 16-17) | R/W |

| 2    | Resets max word count register               | W   |

#### $Max \ event \ count \ (ROSMEM + 0x0A)$

Default value = 0x00Reset by a hard reset.

| bits | Description              | acc |

|------|--------------------------|-----|

| 0-15 | Maximum number of events | R/W |

#### <u>Cycle count (ROSMEM + 0x0C)</u>

Default value = 0x00Reset by a hard reset.

| bits   | description                                 | acc |

|--------|---------------------------------------------|-----|

| 0 - 15 | Number of cycles to repeat the transmission | R/W |

If number of cycles is set to 0, then 65536 cycles (0x10000) will be performed.

#### 5.2.3 CEROS 0-4

CEROSX is replaced by the base address of the corresponding CEROS. Note that CEROS 4 only has one channel (related information is located in the least significant bit).

#### LOCK/MASK (CEROSX + 0x00)

| bits  | description          | acc |                                 | Signal that resets |

|-------|----------------------|-----|---------------------------------|--------------------|

| 0-5   | Channel UNLOCK       | R   | 1 = channel is unlocked         | Soft reset         |

| 6-11  | MASK Channel         | R/W | 1 = channel masked              | Hard reset         |

| 12-14 | CEROS identification | R   | 0 for ceros 0, 1 for ceros 1, 2 |                    |

|       |                      |     | for ceros 2, 3 for ceros 3, 4   |                    |

|       |                      |     | for ceros 4                     |                    |

#### DISABLE REGISTER (CEROSX + 0x02)

Default value = 0x84Reset by a hard reset.

| bits  | Description                                                | Acc |

|-------|------------------------------------------------------------|-----|

| 0     | Disable NOT LOCK to block channel                          | R/W |

| 1     | Disable HAS UNLOCK to block channel                        | R/W |

| 2     | Disable TIMED OUT or max words to block channel            | R/W |

| 3     | Disable FIFO Full to block channel                         | R/W |

| 4     | Disable send PAF warning word within the data.             | R/W |

| 5     | Disable send EVID misalignment error word within the data. | R/W |

| 6     | Enable send HPTDC data although there are no hits.         | R/W |

| 7     | Disable EVID misalignment to block channel                 | R/W |

| 10-15 | Channel blocked                                            | R   |

If for any reason the ROS blocks automatically one of the channels, it will be signalled with a 1 in the Channel blocked field. A channel will appear as blocked either because the user has masked it by writing in register LOCK/MASK or due to any of the following malfunctions:

- The channel is unlocked and the option "Disable not lock to block channel" was set to 0.

- The channel has unlocked at any time (although at the moment is again locked) and the option "Disable has unlock to block channel" was set to 0.

- The channel has timed out and the option "Disable time-out or max words to block channel" was set to 0.

- More than 200 consecutive words have been read out from that channel without finding a ROB trailer and the option "Disable time-out or max words to block channel" was set to 0.

- The FIFO of that channel has been full and the option "Disable FIFO full" was set to 0.

- There has been an Event Identification misalignment in that channel and the option "Disable EVID misalignment to block channel" was set to 0.

#### TIMEDOUT / HASUNLOCK (CEROSX + 0x04)

Reset by a soft reset.

| bits | Description                       | acc |

|------|-----------------------------------|-----|

| 0-5  | Channel has TIMED OUT / MAX WORDS | R/W |

| 6-1  | Channel HAS UNLOCK                | R/W |

There are two reasons why a channel can signal a timeout:

- The FIFO is empty longer than the timeout value programmed for that group of 6 channels (register TIMEOUT VALUE). Therefore, the programmed timeout should be long enough to cope with the different latency of the L1A signal between the Minicrates and the ROS and include also the propagation time between the cooper links from Minicrates to ROS.

- The number of consecutive 32 bits words read from a channel is over the programmed limit (by default 200 words ( $\sim 10 \, \mu s$ )) and no ROB trailer has been found.

#### PAF (CEROSX + 0x06)

Reset by a soft reset.

| bits | Description           | acc |                                                   |

|------|-----------------------|-----|---------------------------------------------------|

| 0-5  | FIFO's PAF            | R   | = 1 an Almost Full condition has been achieved in |

|      |                       |     | the FIFO of the corresponding channel.            |

| 6-11 | FIFO's PAF REGISTERED | R/W | Registered value of the previous.                 |

# EF (CEROSX + 0x08)Reset by a soft reset.

| bits | description                 | acc |                                                      |

|------|-----------------------------|-----|------------------------------------------------------|

| 0-5  | FIFO's EF                   | R   | 1 = FIFO is empty                                    |

| 6-11 | Event ID misalignment error | R/W | 1 = that channel had an event ID misalignment error. |

| bits | description      | acc |                                                          |

|------|------------------|-----|----------------------------------------------------------|

| 0-5  | Maxwords reached | R   | 1 = The maximum number of words in that channel has been |

|      |                  |     | received and no ROB trailer has been found.              |

| 6-   | FIFO's FF        | R/W | 1 = FIFO has been full at any time.                      |

| 11   | REGISTERED       |     | ·                                                        |

#### <u>PAF VALUE (CEROSX + $\theta x \theta C$ )</u>

Default value = 0x200Reset by a hard reset.

|   | bits | description                                                                               | acc |                                                                       |  |  |  |

|---|------|-------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------|--|--|--|

| ĺ | 0-10 | 0-10   FIFO's PAF VALUE   R/W   When the number of empty 16 bits words in a FIFO is small |     |                                                                       |  |  |  |

|   |      |                                                                                           |     | this value, the FIFO will set to 1 the PAF flag. This value is common |  |  |  |

|   |      |                                                                                           |     | all channels in a CEROS.                                              |  |  |  |

| Ī | 11   | RECEIVERS OFF                                                                             | R/W | = 1 the 6 channels will turn off their receivers, so no data will be  |  |  |  |

|   |      |                                                                                           |     | received.                                                             |  |  |  |

The 2kwords input FIFO for each channel has a flag (PAF flag) to signal that the number of empty positions at the FIFO is smaller than a programmed limit, the PAF value.

By default, the PAF value at the FIFOs after a Master Reset (MRS) is 15, that is, when the number of words in the FIFO is larger than 2049-15 = 2034, the PAF flag will be set to 1.

In order to program a new PAF value, it is necessary to write the desired PAF value in this register (at each CEROS) and then write a 1 in bit 11 of register ROSVME+0x00 to download the new value into the FIFOs. During this task, the channels will be unlocked, so before taking data again, the TIMEDOUT/HASUNLOCK register should be erased.

If a Master CEROS FIFO reset (MRS) is performed, the programmed PAF value in the FIFOs will be erased. To empty the data in a FIFO without erasing the programmed PAF value, a Partial CEROS FIFO reset (PRS) should be used instead.

#### FIFO WORD PARITY (CEROSX + 0x0E)

Reset by a hard reset.

| bits | description      | acc |                                                                      |

|------|------------------|-----|----------------------------------------------------------------------|

| 0-15 | FIFO WORD PARITY | R/W | = 1 a parity error has been detected in a word. The position of that |

|      |                  |     | word in the data stream is the same as the corresponding position    |

|      |                  |     | of the parity bit in this register.                                  |

This is a shift register where it is stored the parity errors of the 16 bits words read from the FIFO, starting from the least significant bit.

#### FIFO BYTE PARITY 0 (CEROSX + 0x10)

Reset by a hard reset.

| bits | description                | acc |

|------|----------------------------|-----|

| 0-15 | FIFO BYTE PARITY bits 0-15 | R/W |

#### FIFO BYTE PARITY 1 (CEROSX + 0x12)

Reset by a hard reset.

| bits | description                 | acc |

|------|-----------------------------|-----|

| 0-15 | FIFO BYTE PARITY bits 16-31 | R/W |

In these two registers, the actual parity and not the parity error is shifted starting by the least significant bit. In this case, each bit corresponds to the parity of a byte and not of a 16 bits word.

#### FIFO DISPARITY COUNTER (CEROSX + 0x14)

Default value = 0x0Reset by a hard reset.

| bits | description            | acc |

|------|------------------------|-----|

| 0-15 | FIFO DISPARITY COUNTER | R/W |

Each time a parity error is found in any of the channels of a CEROS, this counter will be incremented. (Warning, this counter may overflow).

#### TIMEOUT VALUE(CEROSX + 0x16)

Default value = 0xFFF (102,4  $\mu s$ ) Reset by a hard reset.

|   | bits | description                                   | acc |        |    |       |        |

|---|------|-----------------------------------------------|-----|--------|----|-------|--------|

| Ī | 0-11 | TIME OUT VALUE for all channels of this CEROS | R/W | Number | of | clock | cycles |

before timeout.

This value corresponds to the number of 40 MHz clock cycles that the ROS will wait when it is reading a channel but its FIFO is empty.

#### MAXWORDS LIMIT (CEROSX + 0x18)

Default value = 0x1FF (no limit)

Reset by a hard reset.

| bits | Description                                    | acc |                             |

|------|------------------------------------------------|-----|-----------------------------|

| 0-7  | Maximum number of blocks of 8 32-bit words per | R/W |                             |

|      | channel to be read.                            |     |                             |

| 8    | No limit                                       | R/W | =1 there is no limit in the |

|      |                                                |     | maximum number of words.    |

In this register you can program how many multiples of 8 words (32 bit) per ROB channel you want to read. It does not take into account headers and trailers, therefore, it only limits the number of hits or error words.

The minimum programmed number is 8 words, and the maximum is 4095 words.

It might be important to set a limit to the maximum number of ROBs in order to avoid a situation in which it is impossible to find the ROB trailer and the ROS gets stuck reading nonsense data (for example a link that is faulty and is sending nonsense data).

#### FIFO PAF COUNTER 0-5 (CEROSX + 0x20-2A)

Default value = 0x0. Reset by a soft reset.

| bits | description          | acc |

|------|----------------------|-----|

| 0-15 | FIFO 0-5 PAF counter | R/W |

It counts the number of times that the programmed almost full limit has been achieved in a particular channel of that CEROS.

#### FIFO DATA 0-5 (CEROSX + 0x30-3A)

| bits | description   | acc |

|------|---------------|-----|

| 0-15 | FIFO 0-5 data | R   |

#### TO BE USED ONLY FOR DEBUGING.

By reading at this register, the data from the corresponding channel is taken out from the input FIFO, that is, once read, <u>it cannot be read again</u>. When all the data have been read, the Empty FIFO flag will be signalled and the last word read will remain at the FIFO output, so the same value will be read again in following accesses.

Note that data read from this register has the HPTDC data format, and therefore, there is no indication of the number of channel that is being read.

#### PAE/PAF PROGRAMMED 0-5 (CEROSX + 0x40-4A)

|      | 0.0000                      | acc |

|------|-----------------------------|-----|

| 0-10 | FIFO 0-5 PAE/PAF programmed | R   |

The PAF value programmed at each FIFO can be read from these registers.

This register **should only be accessed during configuration, not during data acquisition,** otherwise data at the FIFOs can be corrupted.

#### $TTS (CEROSX + \theta x5\theta)$

Default value = 0x1FReset by a hard reset.

| bits | description                            | acc |

|------|----------------------------------------|-----|

| 0    | Resynch if timeout                     | R/W |

| 1    | Resynch if event ID misalignment       | R/W |

| 2    | Warning overflow if PAF                | R/W |

| 3    | Resynch if Fifo Full                   | R/W |

| 4    | Resynch if max number of words reached | R/W |

When setting these bits to 1, you enable to set a flag bit in the error words that the ROS sent (see later). This bit will be processed by the DDU and will force the TTS transitions in the DDU TTS state machine.

#### **5.2.4 ROSCTRL**

#### CEROS or SC TIMED OUT (ROSCTRL + $\theta x \theta \theta$ )

Default value = 0x00Reset by a soft reset.

|     | description                                    | acc |

|-----|------------------------------------------------|-----|

| 0-4 | CEROS timed out                                | R/W |

| 5   | SECTOR COLLECTOR channel has timed out         | R/W |

| 6   | SECTOR COLLECTOR channel FIFO full registered. | R/W |

| 7   | Bunch ID FIFO full registered.                 | R/W |

| 8   | Event ID HIGH FIFO full registered.            | R/W |

| 9   | Event ID LOW FIFO full registered.             | R/W |

The Sector Collector channel is not blocked if at any time its FIFO is full, but some words may be lost. At the moment, the Sector Collector FIFO is 511 words (16 bits) deep, so it should be large enough to cope with the data received from the Sector Collector for 1 event.

#### MASKS (ROSCTRL + 0x02)

Default value = 0x5D40Reset by a hard reset.

| bits | description                                                          | acc |

|------|----------------------------------------------------------------------|-----|

| 0-4  | Mask CEROS                                                           | R/W |

| 5    | Enable SECTOR COLLECTOR channel                                      | R/W |

| 6    | Disable TIMED OUT to mask CEROS or SECTOR COLLECTOR channel          | R/W |

| 7    | Enable reception of AUTOL1A trigger at ROS                           | R/W |

| 8    | Disable reception of TTC L1A trigger from TIM module.                | R/W |

| 9    | Select ROS internal Event ID counter                                 | R/W |

| 10   | Enable send BUNCH COUNTER debugging word within the data flow.       | R/W |

| 11   | Enable send BUNCH RESET COUNTER debugging word within the data flow. | R/W |

| 12   | Enable send L1A Warning overflow bit in the data                     | R/W |

| 13   | Read Internal SECTOR COLLECTOR FIFO (to be used for debugging)       | R/W |

| 14   | Resynch if Ceros has timedout                                        | R/W |

| 15   | Generate local VME trigger at ROS.                                   | W   |

Note that the TTC L1A is disabled by default at a reset to allow proper configuration of the ROS although the TTC system is sending L1As.

The bit number 13, for reading internal Sector Collector FIFO should be set only for debugging purposes. If it is set, the ROS\_READY-TRIGGER\_STROBE handshake will not take place.

Bit number 9, "Select local Event ID counter" should be used either for debugging purposes when there is no TTC or TIM boards present, or when the L1A comes from the Sector Collector board (AutoL1A). In such a case, L1As from the TIM board should be disabled (bit 8 to 0).

Bits 12 and 14 are used to flag the corresponding bit in the data that will be processed by the DDU in order to modify the status of its TTS state machine.

#### $TIMEOUT\ VALUE\ (ROSCTRL + 0x04)$

Default value =  $0xFFF (102,4 \mu s)$

Reset by a hard reset.

| bits | description                                           | acc |

|------|-------------------------------------------------------|-----|

| 0-11 | TIME OUT VALUE for CEROS and SECTOR COLLECTOR channel | R/W |

For the Sector Collector channel, this value represents the number of clock cycles since the ROS\_READY signal was set to 1 until a timeout is given because there has been no TRG\_STROBE signal from the Sector Collector board.

For the CEROS module, this value should be larger than the maximum number of cycles needed for processing one event in one channel (0x190  $\sim$ 10  $\mu$ s).

The programmed value should match the larger of these two timeouts.

BUNCH NUMBER (ROSCTRL + 0x06)

| bits | description                   | acc |                                        |

|------|-------------------------------|-----|----------------------------------------|

| 0-11 | Read last BUNCH NUMBER        | R   |                                        |

| 0-11 | Write BUNCH NUMBER in FIFO    | W   | Should be used only for ROS debugging. |

| 12   | Bunch ID fifo full registered | R/W | Reset by a soft reset.                 |

EVENT LOW NUMBER (ROSCTRL + 0x08)

| bits | description                       | acc |                                        |

|------|-----------------------------------|-----|----------------------------------------|

| 0-11 | Read last EVENT LOW NUMBER        | R   |                                        |

| 0-11 | Write EVENT LOW NUMBER in FIFO    | W   | Should be used only for ROS debugging. |

| 12   | Event ID low fifo full registered | R/W | Reset by a soft reset.                 |

EVENT HIGH NUMBER (ROSCTRL + 0x0A)

| bits | description                        | acc |                                        |

|------|------------------------------------|-----|----------------------------------------|

| 0-11 | Read last EVENT HIGH NUMBER        | R   |                                        |

| 0-11 | Write EVENT HIGH NUMBER in FIFO    | W   | Should be used only for ROS debugging. |

| 12   | Event ID high fifo full registered | R/W | Reset by a soft reset.                 |

SECTOR COLLECTOR DATA (ROSCTRL + 0x0C)

| bits | description                     |   |                             |

|------|---------------------------------|---|-----------------------------|

| 0-15 | Write SECTOR COLLECTOR data in  | W | Should be used only for ROS |

|      | SECTOR COLLECTOR FIFO           |   | debugging.                  |

| 0-8  | SECTOR COLLECTOR FIFO occupancy |   |                             |

|      | (16 bits words)                 |   |                             |

| 12 | Sector Collector fifo full registered | R/W | Reset by a soft reset. |  |

|----|---------------------------------------|-----|------------------------|--|

|----|---------------------------------------|-----|------------------------|--|

#### <u>BUNCH COUNTER FIFO OCCUPANCY (ROSCTRL + 0x0E)</u>

Reset by a hard reset.

| I | bits | description                                     | acc |

|---|------|-------------------------------------------------|-----|

|   | 0-7  | BUNCH COUNTER FIFO maximum occupancy registered | R   |

#### <u>EVENT COUNTER FIFO OCCUPANCY (ROSCTRL + 0x10)</u>

Reset by a hard reset.

| bits | description                                  | acc |

|------|----------------------------------------------|-----|

| 0-7  | EVENT LOW FIFO maximum occupancy registered  | R   |

| 8-15 | EVENT HIGH FIFO maximum occupancy registered | R   |

These two registers store the maximum occupancy of the corresponding FIFOs since last global reset.

These FIFOs are 255 words deep, and store the Bunch and Event counter values received from the TIM module through the TIM backplane. Once the ROS has finished processing one event, it will look at these FIFOs to see if there is any event pending and will start processing it. Therefore, if these FIFOs are full at any time, some L1As may be lost.

#### L1A FIFO THRESHOLD (ROSCTRL + 0x12)

Reset by a hard reset.

Default value 0x10 (16 L1As)

| bits | description               | acc |

|------|---------------------------|-----|

| 0-7  | Threshold of the L1A FIFO | R/W |

In this register you can program the threshold over which the ROS will send a L1A FIFO Warning Overflow error .

#### ORBIT LOW COUNTER (ROSCTRL + 0x14)

Reset by a hard reset.

|      |                           | acc |

|------|---------------------------|-----|

| 0-15 | Orbit counter (bits 0-15) | R/W |

#### <u>ORBIT HIGH COUNTER (ROSCTRL + 0x16)</u>

Reset by a hard reset.

|     | 1 1 1                      | acc |

|-----|----------------------------|-----|

| 0-7 | Orbit counter (bits 16-23) | R/W |

These registers are internal counters in the ROS that is incremented at each Bunch reset signal, i.e., it will count the number of orbits. This value can be sent within the data flow in the Bunch reset counter debugging word.

#### <u>EVENT ID COUNTER (ROSCTRL + 0x18)</u>

Default value = 0xFFF

Reset by a soft reset and by an event reset signal from the TTC.

| bits | description      | acc |

|------|------------------|-----|

| 0-11 | Event ID counter | R/W |

This register is an internal counter in the ROS that is incremented when a L1A is received from any of the sources only if they have been enabled, that is:

- Local L1A generated from a VME access (bit 15 of register ROSCTRL+0x02).

- AutoL1A from the SECTOR COLLECTOR (Only if it has been enabled by writing a 1 on bit 7 of register ROSCTRL+0x02).

- L1A from the TTC system. (Only if it has been enabled by writing a 0 on bit 8 of register ROSCTRL+0x02).

This is the event ID that will be sent in the ROS Event Header word if ROS internal Event counter is selected (bit 9 of register ROSCTRL+0x02). Note that as the Event ID received from the TTC system, the first L1A will be marked with Event ID = 0, so in principle its value will be one less than the number of L1As received.

Also, note that if internal event ID is selected, the L1As will not be stored in a FIFO, therefore, if a L1A is received while the ROS is still processing a previous event, the event ID counter will be incremented, and when the ROS finishes, it will start to process the next event with the event ID value that it reads from the counter, so an event ID misalignment will happen.

#### COMMAND (ROSCTRL + 0x1A)

Reset by a hard reset.

| bits | description                    | acc |

|------|--------------------------------|-----|

| 0-3  | Command received from the TTC. | R/W |

#### MAX EVENT SIZE (ROSCTRL + 0x1C)

Reset by a hard reset.

| bits | description                  | acc |

|------|------------------------------|-----|

| 0-15 | Maximum size of a ROS event. | R   |

# **6 ROS-25 CONFIGURATION**

# 6.1 Mode of operation: Memory readout.

#### Reset the ROS-25 board.

Write 0xF000 to register ROSVME+ 0x00.

#### Power up the GOL.

Write 0x0 to register ROSVME+ 0x12 to power up the 2.5V power supply.

Wait ~800ms.

Write 0x0 to register ROSVME+ 0x12 to erase all the registered flags.

#### Optional: Mask channels not used.

For example: Mask full ceros 3 (channels from 18 to 23)

Write 0x008 to register ROSCTRL+ 0x02.

Note that this register has other bits that should not be modified unless desired.

Mask channel 16 which corresponds to channel 4 of ceros 2.

Write 0x400 to register CEROS2+ 0x00.

#### **Optional: Write timeout values.**

For example:

Write 0x1FF to register CEROS0+ 0x16.

Write 0x1FF to register CEROS1+ 0x16.

Write 0x1FF to register CEROS2+ 0x16.

Write 0x1FF to register CEROS3+ 0x16.

Write 0x1FF to register CEROS4+ 0x16.

Write 0xFFF to register ROSCTRL+ 0x04.

#### **Optional: Write PAF values**

Write PAF value in register CEROS0 + 0x0C

Write PAF value in register CEROS1 + 0x0C

Write PAF value in register CEROS2 + 0x0C

Write PAF value in register CEROS3 + 0x0C

Write PAF value in register CEROS4 + 0x0C

Load PAF values: Write a 1 in bit 11 of ROSVME + 0x00.

Note that this register has other bits that should not be modified unless desired.

#### Reset timeouts and unlocks flags.

Write 0x0000 to register CEROS0+ 0x04.

Write 0x0000 to register CEROS1+ 0x04.

Write 0x0000 to register CEROS2+ 0x04.

Write 0x0000 to register CEROS3+ 0x04.

Write 0x0000 to register CEROS4+ 0x04.

Write 0x0000 to register ROSCTRL+ 0x00.

#### Optional. Specify different options for disabling channels.

For example: If you want to disable that the ROS-25 sends an error Ev ID word when events are not aligned, you would have to write a 0 in bit 5 of register CEROSX+0x02.

If you want to disable that a channel is blocked when its FIFO is full then you would have to write a 1 on bit 3 of CEROSX+0x02.

#### Optional. Specify maximum number of words to be read per channel.

Write the maximum number of words in register CEROSX + 0x18.

#### Optional. Specify L1A fifo threshold to send error warning overflow.

Write the threshold in ROSCTRL+0x12.

#### **Optional. Specify options for TTS error words.**

Write options in CEROSX+0x50.

#### Optional. Specify options for for FPGA Control register.

Write in ROSVME+0x8.

### Optional. Specify options for Control and Status register

Write in ROSVME+0x0.

#### Write maximum number of 16 bit words or of events to be written in memory.

Write max number words to registers ROSMEM+ 0x06 and ROSMEM+ 0x08.

Write max number of events to register ROSMEM+ 0x0A.

#### Reset memory pointer.

Write 0x0004 to register ROSMEM+ 0x04.

#### **Optional: Program interruptions.**

For example, program interruption by "memory done" at level 2 with an interruption vector of 0xC4:

Write 0xC444 at ROSVME + 0x06.

#### Specify options for ROSCTRL and enable L1A:

For example:

Enable sending Bunch ID debug word or bunch reset counter. Write a 1 in bit 10 and 11 of register ROSCTRL+0x02.

If Sector Collector channel wants to be read, bit 5 of ROSCTRL + 0x02 should also bit set to 1.

Furthermore.

At some point before starting the data acquisition a L1A source should be enabled:

- in normal operation mode it will be the TTC L1A, that is bit 7 and bit 8 to 0 in ROSCTRL + 0x02.

- if AUTOL1As are going to be used as trigger signal, bit 7 and bit 8 should be set to 1. In such a case, the bunch and event counters received from the TIM will not have sense, so the Bunch counter and Bunch counter resets words should be disabled (bit 10 and 11 to 0), and also, internal Event counter should be chosen (bit 9 to 1).

#### **Enable transfer mode**

This is the last access that should be done before data acquisition starts. For sending data from the FIFOs to the memory, bit 1 of register ROSMEM+0x00 should be set to 1.

If you want to limit the number of words written to memory you would have to set to 1 also bit 2

Either, if you want to limit the number of events written to memory you would have to set to 1 bit 3.

#### Start the data acquisition.

Send N L1A through the TTC system.

Wait until Memory Done = 1. (bit 1 of register ROSVME+0x00)

If you want to read the memory contents before Memory Done=1 then you would have to disable the transfer from FIFOs to memory. Write a 0 in bit 1 of register ROSMEM+0x00. Read memory pointer.

Read from the memory the number of 16 bits words specified by the memory pointer.

Reset memory pointer.

Enable again the transfer mode.

### 6.2 Check status

In order to check that the readout and the ROS-25 is behaving properly, there are some checking that can also be performed after configuration is done or every once in a while.

- Check that all the FPGAS have been properly loaded. (Read bits 6 to 2 of ROSVME+0x00. If 1, they are ok).

- Check the channel blocked flags. (bits 10 to 15 of CEROSX + 0x02).

- Check the empty FIFO flags.

- Check the event ID misalignment flags. (Register CEROSX + 0x08).

- Check the full FIFO flags. (Register CEROSX + 0x0A). (At least the registered values).

- Check PAF flags. (Register CEROSX + 0x06) (At least the registered values).

• Check if any channel has been unlocked or timedout (register CEROSX+0x04) or the actual lock status (register CEROSX+0x00)

- Check the FIFO disparity counter (CEROSX+0x14)

- Check the FIFOs PAF counters (CEROSX+0x20-0x2a)

- Check the limit of maximum number of words is reached (CEROSX+0x8)

- Check the maximum event size (ROSCTRL+0x01C)

- Check the Bunch, Event Low or Event High counter FIFO maximum occupancy (ROSCTRL+0x0E or ROSCTRL+0x10)

- Check timeouts of the CEROS and of the Sector collector channel.

- Check FIFO full flag of the SECTOR COLLECTOR channel.

- Check FIFO full flags of the Bunch, Event High and Event Low FIFOs. (Register ROSCTRL+0x00)

- Check GOL ready and GOL not ready registered flag and QPLL locked and QPLL unlocked registered flag. (Register ROSVME + 0x12).

# 7 <u>INTERFACE TO THE VOLTAGE, CURRENT AND</u> TEMPERATURE SENSORS.

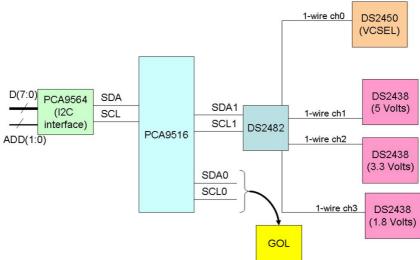

At the ROS there are three sensors that allow measuring each of the three voltages used at this board (5 V, 3.3 V and 1.8 V), measure their corresponding currents and performing temperature monitorization.

These sensors (DS2438) are 1-wire devices, which can be accessed through an I2C to 1-wire interface (DS2482). Channel 0 of the DS2482 is connected to DS2450 device for reading the laser transmitter optical power (this is not explained in this version of the manual). The other three channels are connected as indicated in the table:

| Channel number | Sensor       | VAD   | VDD   | Current |

|----------------|--------------|-------|-------|---------|

| Channel 1      | 5 V sensor   | 5 V   | 3.3 V | 5 V     |

| Channel 2      | 3.3 V sensor | 3.3 V | 3.3 V | 3.3 V   |

| Channel 3      | 1.8 V sensor | 1.8 V | 3.3 V | 1.8 V   |

The VME to I2C interface is implemented through the device PCA9564 [3]. There is only one PCA9564 device to perform I2C access, both to the GOL and to the DS2482 bridge to the sensors. To choose among both I2C buses, a bit has to be enabled on register "I2C & 1-wire & GOL & QPLL (ROSVME+0x12)":

- Write a 1 in bit 0 for enabling access to the GOL.

- Write a 1 in bit 1 for enabling access to the 1-wire sensor.

Setting both bits to 1 is not allowed, having priority the I,V,T 1-wire sensor.

In the following picture, a diagram of how the different devices are interconnected at the ROS is presented:

Figure 7: Diagram of the I2C buses at the ROS.

# 7.1 <u>I2C interface through the PCA9564</u>

As can be seen in its datasheet [3], the PCA9564 device has 4 registers (Status, Data, Own address and Control), which can be accessed directly as ROS registers. Here we present again the corresponding registers at the ROS for the PCA9564 used for reading the sensors and for the PCA9564 used for interface with the GOL. (Remember that ROSVME=ROS Base Address + 0x380).

### PCA STATUS (ROSVME + 0x20)

| bits | description | acc | default |

|------|-------------|-----|---------|

| 0-7  | Status      | R   | 0xF8    |

| 0-7  | Time-out    | W   | 0xFF    |

### PCA DATA (ROSVME + 0x22)

$\overline{\text{Default}} = 0x00$

| bits | description | acc |

|------|-------------|-----|

| 0-7  | Data        | R/W |

# $\underline{PCA} \ \underline{ADDRESS} (ROSVME + 0x24)$

$\overline{Default = 0x00}$

| bits | description | acc |

|------|-------------|-----|

| 0-7  | Own address | R/W |

# $\underline{PCA}$ $\underline{CONTROL}$ $(\underline{ROSVME} + 0x26)$

Default = 0x00

| bits | description | acc | description             |

|------|-------------|-----|-------------------------|

| 7    | AA          | R/W | Assert acknowledge flag |

| 6    | ENSIO       | R/W | SIO enable bit          |

| 5    | STA         | R/W | Start flag              |

| 4    | STO         | R/W | Stop flag               |

| 3    | SI          | R/W | Serial interrupt flag   |

| 2-0  | CR          | R/W | Serial clock rate       |

CR: Serial clock frequency

| 000 | 330 kHz |

|-----|---------|

| 001 | 288 kHz |

| 010 | 217 kHz |

| 011 | 146 kHz |

| 100 | 88 kHz  |

| 101 | 59 kHz  |

| 110 | 44 kHz |

|-----|--------|

| 111 | 36 kHz |

The procedure for writing and reading via I2C is described in the PCA9564 datasheet; however, we include here a summary of routines Write\_PCA(out p\_add, out p\_data) and Read\_PCA (out p\_add, in p\_data), where p\_add is the I2C address of the device you want to communicate with and p\_data is the 7 bit data to send or receive.

The PCA9564 will be used in Master mode in every access; therefore, PCA\_ADDRESS register is not needed.

The first step that has to be done is to enable SIO logic in the device at register PCA\_CONTROL which requires to wait 10 ms before starting any other access. Unless this bit is disabled by the user at some point, this step needs to be done only once at the beginning. At this point, the I2C bit rate can also be selected on this register.

The next steps are summarized in what follows:

#### 12C WRITE ACCESS THROUGH THE PCA9564

Write PCA(out p\_add, out p\_data)

- 1) Check PCA9564 status register, it has to be 0xF8. (Read ROS Base Add + 0x3A0).

- 2) Send START (Write 0x60 in ROS Base Add + 0x3A6).

- 3) Wait until interrupt flag (SI) is asserted. (Read bit 3 of ROS\_Base\_Add + 0x3A6).

- 4) Check status, it has to be 0x08. (Read ROS Base Add + 0x3A0).

- 5) Send the I2C address of the device you want to access to by writing p\_add in bits 7 to 1 and a 0 (write) in bit 0 of PCA\_DATA. (Write p\_add & '0' in ROS\_Base\_Add + 0x3A2).

- 6) Reset SI flag. (Write 0x40 in ROS Base Add + 0x 3A6).

- 7) Wait until interrupt flag (SI) is asserted. (Read bit 3 of ROS Base Add + 0x3A6).

- 8) Check status, it has to be 0x18. (Read ROS\_Base\_Add + 0x3A0).

- 9) Send the data byte that you want to write by writing it in PCA\_DATA. (Write p\_data on ROS Base Add + 0x3A2).

- 10) Reset SI flag. (Write 0x40 in ROS\_Base\_Add + 0x 3A6).

- 11) Wait until interrupt flag (SI) is asserted. (Read bit 3 of ROS Base Add + 0x3A6).

- 12) Check status, it has to be 0x28. (Read ROS Base Add + 0x3A0).

- 13) Send a STOP condition. (Write 0x50 to ROS Base Add + 0x3A6).

- 14) Check status, it has to be 0xF8. (Read ROS\_Base\_Add + 0x3A0).

#### <u>I2C READ ACCESS THROUGH THE PCA9564</u>

Read\_PCA (out p\_add, in p\_data)

- 1) Check PCA9564 status register, it has to be 0xF8. (Read ROS Base Add + 0x3A0).

- 2) Send START (Write 0x60 in ROS\_Base\_Add + 0x3A6).

- 3) Wait until interrupt flag (SI) is asserted. (Read bit 3 of ROS\_Base\_Add + 0x3A6).

- 4) Check status, it has to be 0x08. (Read ROS Base Add + 0x3A0).

- 5) Send the I2C address of the device you want to access to by writing p\_add in bits 7 to 1 and a 1 (read) in bit 0 of PCA\_DATA. (Write p\_add & '0' in ROS\_Base\_Add + 0x3A2).

- 6) Reset SI flag. (Write 0x40 in ROS Base Add + 0x 3A6).

- 7) Wait until interrupt flag (SI) is asserted. (Read bit 3 of ROS Base Add + 0x3A6).

- 8) Check status, it has to be 0x40. (Read ROS\_Base\_Add + 0x3A0).

- 9) Reset SI flag. (Write 0x40 in ROS Base Add + 0x 3A6).

- 10) Wait until interrupt flag (SI) is asserted. (Read bit 3 of ROS Base Add + 0x3A6).

- 11) Read the data received from the device from PCA\_DATA. (Read p\_data from ROS Base Add + 0x3A2).

- 12) Check status, it has to be 0x58. (Read ROS Base Add + 0x3A0).

- 13) Send a STOP condition. (Write 0x50 to ROS Base Add + 0x3A6).

- 14) Check status, it has to be 0xF8. (Read ROS Base Add + 0x3A0).

# 7.2 1-Wire Interface to the DS2438 through the DS2482.

### 7.2.1 Brief introduction to DS2482.

As we said before, in order to retrieve the information from the DS2438 sensor we will use the DS2482 I2C to 1-Wire (1-W) bridge.

As an I2C slave of the PCA9564, the DS2482 has a slave address set by three pins (AD0, AD1, AD2) that, in our case, are connected to ground. Therefore, its address value (*slave-add*) is 0x18 (see datasheet [7]).

From all the DS2482 functionality, only some commands will be necessary:

- "Channel Select" (command code 0xC3), used to select one among the 8 output channels.

- "Set Read Pointer" (command code 0xE1), needed for selecting one of the different internal registers that this chip has. The command must be followed by the code of the specific register which will be used in further commands. (see datasheet for codes of different registers). The execution of other commands may set the read pointer to a different value; therefore, it will be necessary to reassign its value, using this command, before executing another one.

- "1-Wire Reset" (command code 0xB4), used to start the transaction cycle specified by 1-W protocol. In fact, this command should be sent first, before all other commands sent to the DS2438.

- "1-Wire Read Byte" (command code 0x96), used to read 1 byte from the 1-W channel. Before doing this, previous commands should instruct 1-W slave IC to prepare information that is going to be read.

• "1-Wire Write Byte" (command code 0xA5), needed for writing 1 byte to the 1-W slave. It must be followed by the byte to be written in a unique transaction.

Many operations may modify one or more bits on the internal registers of DS2482, but we only need to pay special attention to two of them: "Status Register" and "Read data register".

The "Status Register" has the "1WS" bit (bit number 0) which indicates the status of the channel that is being used in a transaction. If this bit is HIGH, the last command executed is still being processed, so it's not possible to send nor receive data (even commands) to that channel. It's necessary to wait until this bit turns into LOW state (polling it) before executing new commands.

The "Read data register" is used to retrieve data read after a "1-Wire Read Byte" command.

## 7.2.2 Brief introduction to DS2438.

As DS2482, DS2438 has many commands and registers, but not all of them are needed for our purposes. Registers are organized in memory pages (9 bytes in length) instead of individually addressable bytes.

This forces to manage/retrieve complete pages before getting specific bytes, even significant bits. Doing this involves the management of an intermediate memory area, called scratchpad area (with corresponding scratchpad pages), where results must be copied from DS2438 internal registers before being read by the DS2482, or where configuration data must be written before being transferred to internal DS2438 registers.

The most important page is page number 0 that contains the status/configuration register, and six additional registers which store the current, temperature and voltage information (two bytes in length for each one) once the appropriated commands have been executed. So, in fact, we will be reading and writing this page every time. Its very recommended to see DS2438 datasheet to see the specific binary data format of current, voltage and temperature because not all register bits are in use.

Due to the importance of status/configuration register, we include some datasheet paragraphs describing those bits useful for us:

The Status/Configuration Register is a non-volatile read/write byte which defines which features of the DS2438 are enabled and how they will function. The register is formatted as follows:

$\begin{array}{ccc} X \text{ ADB NVB TB AD EE CA IAD} \\ \text{MSb} & \text{LSb} \end{array}$

IAD = Current A/D Control Bit. "1" = the current A/D and the ICA are enabled, and current measurements will be taken at the rate of 36.41 Hz; "0" = the current A/D and the ICA have been disabled. The default value of this bit is a "1" (current A/D and ICA are enabled).

CA = Current Accumulator Configuration. "1" = CCA/DCA is enabled, and data will be stored and can be retrieved from page 7, bytes 4-7; "0" = CCA/DCA is disabled, and page 7 can be used for general EEPROM storage. The default value of this bit is a "1" (current CCA/DCA are enabled).